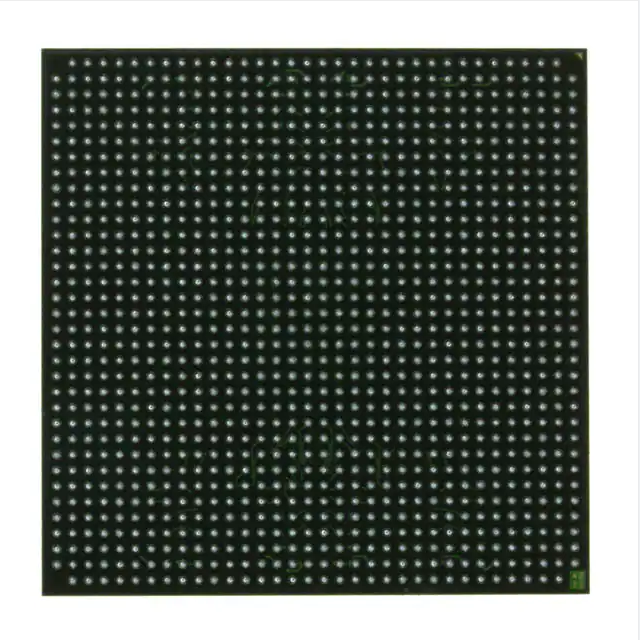

SEESEND מעגלים משולבים מקוריים וחדשים רכיבים אלקטרוניים XC2VP50-6FF1152I

תכונות המוצר

| סוּג | תיאור |

| קטגוריה | מעגלים משולבים (ICs) |

| מר | AMD Xilinx |

| סִדרָה | Virtex®-II Pro |

| חֲבִילָה | מַגָשׁ |

| סטטוס המוצר | מְיוּשָׁן |

| מספר LABs/CLBs | 5904 |

| מספר אלמנטים/תאים לוגיים | 53136 |

| סך סיביות RAM | 4276224 |

| מספר קלט/פלט | 692 |

| אספקת מתח | 1.425V ~ 1.575V |

| סוג הרכבה | מתקן משטח |

| טמפרטורת פעולה | -40°C ~ 100°C (TJ) |

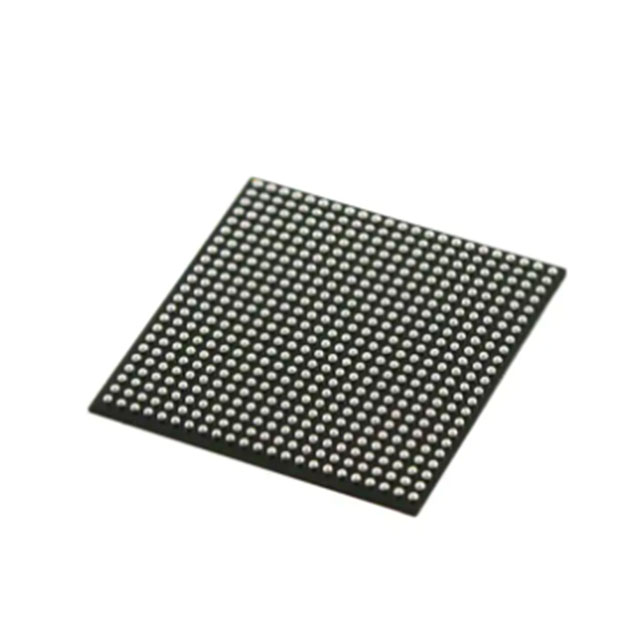

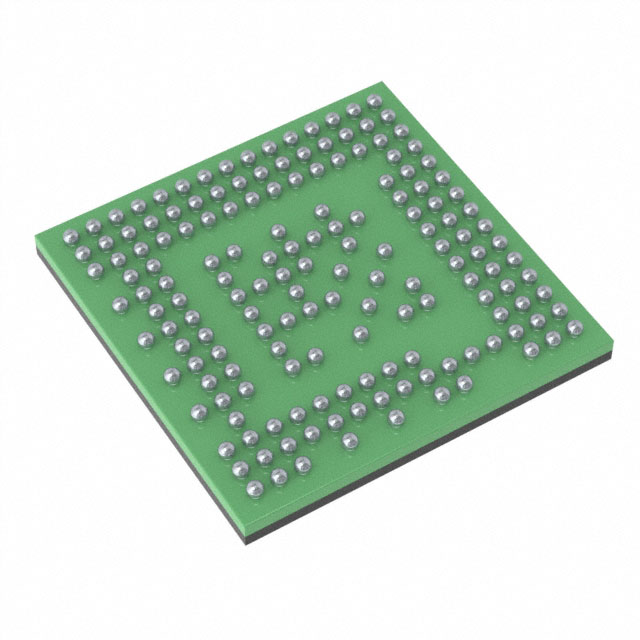

| חבילה / מארז | 1152-BBGA, FCBGA |

| חבילת מכשירי ספק | 1152-FCBGA (35×35) |

| מספר מוצר בסיס | XC2VP50 |

מסמכים ומדיה

| סוג משאב | קישור |

| גיליונות נתונים | Virtex-II Pro, Pro X |

| מידע סביבתי | Xiliinx RoHS אישור |

| התיישנות PCN/ EOL | Mult Dev EOL 6/ינואר/2020 |

| גיליון נתונים HTML | Virtex-II Pro, Pro X |

| דגמי EDA | XC2VP50-6FF1152I מאת Ultra Librarian |

סיווגי סביבה ויצוא

| תְכוּנָה | תיאור |

| מצב RoHS | לא תואם RoHS |

| רמת רגישות לחות (MSL) | 4 (72 שעות) |

| מצב REACH | REACH לא מושפע |

| ECCN | 3A991D |

| HTSUS | 8542.39.0001 |

סקירה כללית של רכיבי FPGA XC2VP50-6FF1152I

משפחות Virtex-II Pro ו- Virtex-II Pro X מכילות פלטפורמות FPGAs עבור עיצובים המבוססים על ליבות IP ומודולים מותאמים אישית.ה-XC2VP50-6FF1152I משלב משדרים מרובי גיגה-ביט ובלוקים של PowerPC CPU בארכיטקטורת Virtex-II Pro Series FPGA.הוא מעניק פתרונות מלאים ליישומי טלקומוניקציה, אלחוטי, רשת, וידאו ו-DSP.

תהליך הנחושת המתקדם בגודל 0.13 מיקרומטר CMOS תשע שכבות וארכיטקטורת Virtex-II Pro מותאמים לעיצובים בעלי ביצועים גבוהים במגוון רחב של צפיפויות.בשילוב מגוון רחב של תכונות גמישות וליבות IP, ה-XC2VP50-6FF1152I משפר את יכולות התכנון הלוגיות הניתנות לתכנות ומהווה אלטרנטיבה רבת עוצמה למערכי שערים מתוכנתים במסכה.

סדרת הרכיבים התעשייתיים של Xilinx XC2VP50-6FF1152I היא 53136 Logic Cells 16 Rocket IOs 2 Power, View Substitutes & Alternatives יחד עם גליונות נתונים, מלאי, תמחור ממפיצים מורשים ב-FPGAkey.com, ותוכלו גם לחפש מוצרים אחרים של FPGAs.

מאפיינים

פתרון FPGA פלטפורמה בעלת ביצועים גבוהים, כולל

עד עשרים משדרים משובצים של RocketIO או RocketIO X Multi-Gigabit (MGT)

עד שני בלוקים של מעבד IBM PowerPC RISC

מבוסס על טכנולוגיית Virtex-II Platform FPGA

משאבי לוגיקה גמישים

תצורת מערכת מבוססת SRAM

טכנולוגיית Interconnect Active

היררכיית זיכרון SelectRAM+

בלוקי מכפיל ייעודיים של 18 סיביות על 18 סיביות

מעגל ניהול שעון בעל ביצועים גבוהים

טכנולוגיית SelectI/O-Ultra

XCITE עכבה בשליטה דיגיטלית (DCI) I/O