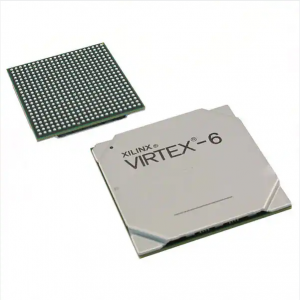

חדש ומקורי XC6VLX240T-2FFG1759I מעגל משולב

תכונות המוצר

| סוּג | תיאור |

| קטגוריה | מעגלים משולבים (ICs) |

| מר | AMD Xilinx |

| סִדרָה | Virtex®-6 LXT |

| חֲבִילָה | מַגָשׁ |

| סטטוס המוצר | פָּעִיל |

| מספר LABs/CLBs | 18840 |

| מספר אלמנטים/תאים לוגיים | 241152 |

| סך סיביות RAM | 15335424 |

| מספר קלט/פלט | 720 |

| אספקת מתח | 0.95V ~ 1.05V |

| סוג הרכבה | מתקן משטח |

| טמפרטורת פעולה | -40°C ~ 100°C (TJ) |

| חבילה / מארז | 1759-BBGA, FCBGA |

| חבילת מכשירי ספק | 1759-FCBGA (42.5×42.5) |

| מספר מוצר בסיס | XC6VLX240 |

מסמכים ומדיה

| סוג משאב | קישור |

| גיליונות נתונים | גיליון נתונים Virtex-6 FPGA |

| מודולי הדרכה למוצרים | סקירה כללית של Virtex-6 FPGA |

| מידע סביבתי | Xiliinx RoHS אישור |

| עיצוב/מפרט PCN | הודעה ללא עופרת חוצה ספינות 31/אוקטובר/2016 |

סיווגי סביבה ויצוא

| תְכוּנָה | תיאור |

| מצב RoHS | תואם ROHS3 |

| רמת רגישות לחות (MSL) | 4 (72 שעות) |

| מצב REACH | REACH לא מושפע |

| ECCN | 3A001A7A |

| HTSUS | 8542.39.0001 |

סקירה כללית של רכיבי FPGA XC6VLX240T-2FFG1759I

XC6VLX240T-2FFG1759I FPGAs הם בסיס הסיליקון הניתן לתכנות עבור פלטפורמות עיצוב ממוקדות המספקות רכיבי תוכנה וחומרה משולבים כדי לאפשר למעצבים להתמקד בחדשנות ברגע שמחזור הפיתוח שלהם מתחיל.באמצעות הארכיטקטורה מבוססת העמודות של הדור השלישי ASMBL (Advanced Silicon Modular Block), ה-XC6VLX240T-2FFG1759I של Xilinx מכיל בלוקים מובנים רבים ברמת המערכת.תכונות אלו מאפשרות למעצבי לוגיקה לבנות את הרמות הגבוהות ביותר של ביצועים ופונקציונליות במערכות מבוססות FPGA שלהם.הבנויים על טכנולוגיית תהליך נחושת חדישה של 40 ננומטר, XC6VLX240T-2FFG1759I FPGAs הם אלטרנטיבה ניתנת לתכנות לטכנולוגיית ASIC מותאמת אישית.מציעים את הפתרון הטוב ביותר למתן מענה לצרכים של מעצבי לוגיקה בעלי ביצועים גבוהים, מעצבי DSP בעלי ביצועים גבוהים, ומעצבי מערכות משובצות בעלות ביצועים גבוהים עם יכולות לוגיקה, DSP, קישוריות ומיקרו-מעבד רך חסרי תקדים.

XC6VLX240T-2FFG1759I מסדרת Xilinx FPGA (מערך שערים לתכנות שדה) הוא Virtex-6 LXT FPGA 720 I/O 1759FCBGA, הצג תחליפים וחלופות יחד עם גיליונות נתונים, מלאי, תמחור ממפיצים מורשים ב-FPGAkey.com, אתה יכול גם לחפש ו, מוצרי FPGAs אחרים.

מאפיינים

שלוש תת-משפחות:

Virtex-6 LXT FPGAs: לוגיקה בעלת ביצועים גבוהים עם קישוריות טורית מתקדמת

Virtex-6 SXT FPGAs: יכולת עיבוד אותות הגבוהה ביותר עם קישוריות טורית מתקדמת

Virtex-6 HXT FPGAs: קישוריות טורית ברוחב הפס הגבוה ביותר

תאימות בין תת-משפחות

התקני LXT ו-SXT תואמים את טביעת הרגל באותה חבילה

FPGA Logic מתקדם, בעל ביצועים גבוהים

טכנולוגיית טבלת חיפוש אמיתית עם 6 כניסות (LUT).

אפשרות LUT5 כפולה (5 כניסות LUT).

זוג כפכפים LUT/כפולים עבור יישומים הדורשים מיקס ריסטר עשיר

יעילות ניתוב משופרת

אפשרות זיכרון RAM מבוזר של 64 סיביות (או שניים של 32 סיביות) לכל LUT של 6 כניסות

SRL32/Dual SRL16 עם אפשרות יציאות רשומות

מנהלי שעונים חזקים עם מצב מעורב (MMCM)

בלוקים של MMCM מספקים חציצה בהשהייה אפסית, סינתזת תדרים, הסטת פאזות שעון, סינון ריצוד כניסה וחלוקת שעון תואמת פאזה

זיכרון RAM/FIFO בלוק של 36Kb

טכנולוגיית SelectIO מקבילה בעלת ביצועים גבוהים

פרוסות DSP48E1 מתקדמות

אפשרויות תצורה גמישות

ממשק SPI ו-Parallel Flash

תמיכה בריבוי סיביות עם לוגיקה ייעודית של תצורה מחדש של תצורה חוזרת

זיהוי אוטומטי של רוחב האוטובוס

יכולת ניטור מערכת בכל המכשירים

ניטור תרמית ומתח אספקה על-שבב/מחוץ לשבב

גישת JTAG לכל הכמויות המנוטרות

בלוקי ממשק משולבים עבור עיצובי PCI Express

משדרים GTX: עד 6.6 ג'יגה-בייט לשנייה

קצבי נתונים מתחת ל-480 Mb/s נתמכים על ידי דגימת יתר בלוגיקת FPGA.

מקלטי משדר GTH: 2.488 Gb/s עד מעבר ל-11 Gb/s

בלוק Ethernet MAC משולב 10/100/1000 Mb/s

תומך ב-1000BASE-X PCS/PMA ו-SGMII באמצעות מקלטי משדר GTX

תומך ב-MII, GMII ו-RGMII באמצעות משאבי טכנולוגיית SelectIO

תמיכה של 2500Mb/s זמינה

טכנולוגיית תהליך CMOS נחושת 40 ננומטר

מתח ליבה של 1.0V (-1, -2, -3 דרגות מהירות בלבד)

אפשרות מתח ליבה בעוצמה נמוכה יותר של 0.9V (דרגת מהירות-1L בלבד)

אריזת Flip Chip עם שלמות אות גבוהה זמינה באפשרויות חבילה סטנדרטית או ללא Pb