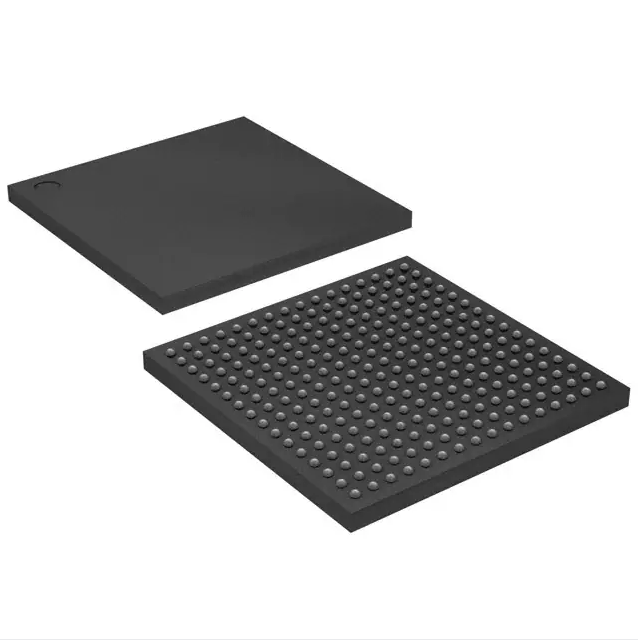

XCZU19EG-2FFVC1760E 100% חדש ומקורי DC ל DC ממיר ושבב ווסת מיתוג

תכונות המוצר

| מאפיין מוצר | ערך תכונה |

| יַצרָן: | Xilinx |

| קטגוריית מוצר: | SoC FPGA |

| הגבלות משלוח: | מוצר זה עשוי לדרוש תיעוד נוסף לייצוא מארצות הברית. |

| RoHS: | פרטים |

| סגנון הרכבה: | SMD/SMT |

| חבילה / מארז: | FBGA-1760 |

| הליבה: | ARM Cortex A53, ARM Cortex R5, ARM Mali-400 MP2 |

| מספר ליבות: | 7 ליבות |

| תדירות שעון מקסימלית: | 600 מגה-הרץ, 667 מגה-הרץ, 1.5 גיגה-הרץ |

| זיכרון הוראות מטמון L1: | 2 x 32 kB, 4 x 32 kB |

| זיכרון נתונים מטמון L1: | 2 x 32 kB, 4 x 32 kB |

| גודל זיכרון תוכנית: | - |

| גודל זיכרון RAM נתונים: | - |

| מספר אלמנטים לוגיים: | 1143450 LE |

| מודולי לוגיקה אדפטיבית - ALMs: | 65340 ALM |

| זיכרון מוטבע: | 34.6 מגהביט |

| מתח אספקת הפעלה: | 850 mV |

| טמפרטורת עבודה מינימלית: | 0 C |

| טמפרטורת עבודה מקסימלית: | + 100 C |

| מותג: | Xilinx |

| זיכרון RAM מבוזר: | 9.8 מגהביט |

| RAM בלוק משובץ - EBR: | 34.6 מגהביט |

| רגיש ללחות: | כן |

| מספר בלוקים של מערך לוגי - LABs: | 65340 LAB |

| מספר משדרים: | 72 מקלט משדר |

| סוג המוצר: | SoC FPGA |

| סִדרָה: | XCZU19EG |

| כמות מארז במפעל: | 1 |

| קטגוריית משנה: | SOC - מערכות על שבב |

| שם מסחרי: | Zynq UltraScale+ |

סוג מעגל משולב

בהשוואה לאלקטרונים, לפוטונים אין מסה סטטית, אינטראקציה חלשה, יכולת אנטי-הפרעות חזקה ומתאימים יותר להעברת מידע.חיבור אופטי צפוי להפוך לטכנולוגיית הליבה לפרוץ את קיר צריכת החשמל, קיר האחסון וקיר התקשורת.התקני תאורה, מצמד, מאפנן, מוליך גל משולבים בתכונות האופטיות בצפיפות גבוהה כגון מערכת מיקרו משולבת פוטו-אלקטרית, יכולים לממש איכות, נפח, צריכת חשמל של אינטגרציה פוטו-אלקטרית בצפיפות גבוהה, פלטפורמת אינטגרציה פוטו-אלקטרית הכוללת מוליכים למחצה מונוליטי משולבים III - V מורכבים (INP ) פלטפורמת אינטגרציה פסיבית, פלטפורמת סיליקט או זכוכית (מוליך גל אופטי מישורי, PLC) ופלטפורמה מבוססת סיליקון.

פלטפורמת InP משמשת בעיקר לייצור לייזר, אפנן, גלאי והתקנים פעילים אחרים, רמת טכנולוגיה נמוכה, עלות מצע גבוהה;שימוש בפלטפורמת PLC לייצור רכיבים פסיביים, הפסד נמוך, נפח גדול;הבעיה הגדולה ביותר בשתי הפלטפורמות היא שהחומרים אינם תואמים לאלקטרוניקה מבוססת סיליקון.היתרון הבולט ביותר של אינטגרציה פוטונית מבוססת סיליקון הוא שהתהליך תואם לתהליך CMOS ועלות הייצור נמוכה, כך שהוא נחשב לערכת האינטגרציה האופטו-אלקטרונית הפוטנציאלית ביותר ואפילו אופטית כולה.

קיימות שתי שיטות אינטגרציה להתקנים פוטוניים מבוססי סיליקון ולמעגלי CMOS.

היתרון של הראשון הוא שניתן לבצע אופטימיזציה של המכשירים הפוטונים והמכשירים האלקטרוניים בנפרד, אך האריזה שלאחר מכן קשה והיישומים המסחריים מוגבלים.את האחרון קשה לתכנן ולעבד אינטגרציה של שני המכשירים.נכון לעכשיו, הרכבה היברידית המבוססת על אינטגרציה של חלקיקים גרעיניים היא הבחירה הטובה ביותר